Personal: https://raintown.org

Personal: satnam@raintown.org

Personal: satnam6502@gmail.com

Professional: s.singh@acm.org

Professional: s.singh@ieee.org

Website: https://satnam6502.github.io

FP Castle: https://fpcastle.com

satnam6502

satnam6502

satnam6502

satnam6502

satnam6502.bsky.social

satnam6502.bsky.social

satnam6502

satnam6502

Google Scholar

Google Scholar

ORCID-ID: 0000-0002-2017-4310

ORCID-ID: 0000-0002-2017-4310

Researchr Profile

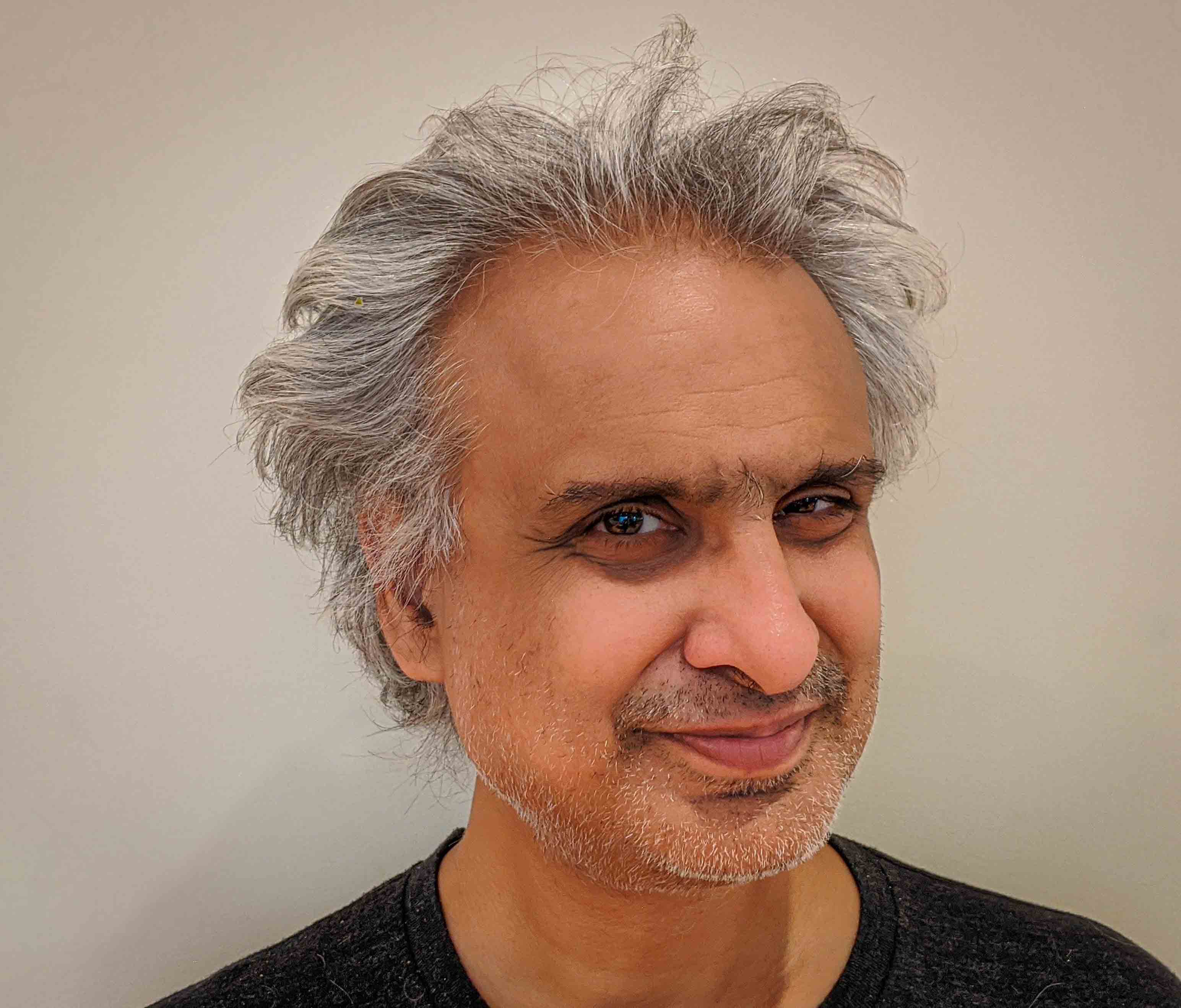

Satnam Singh

I’m currently an independent software engineer working at the intersection of programming languages, hardware design and formal methods. In November 2025 I will join a startup called Harmonic to apply Lean-based formal verification to computer hardware.

Previously I was a computer scientist and hardware engineer working for the AI chip company Groq in California that deploys LLMs (large language models) at scale with very low latency. There I worked on the design of hardware for the power management of machine learning inference chips, the formal verification of machine learning hardware, and the front-end components of a compiler for machine learning models.

I previously worked at Google (machine learning chips, cluster management, formal verification for a silicon root of trust), Facebook (Android optimization), Microsoft (parallel and concurrent programming, hardware synthesis and formal verification) and Xilinx (Lava DSL for hardware design, formal verification of hardware). I started my career as an academic at the University of Glasgow (FPGA-based application acceleration and functional programming, software-defined radio).

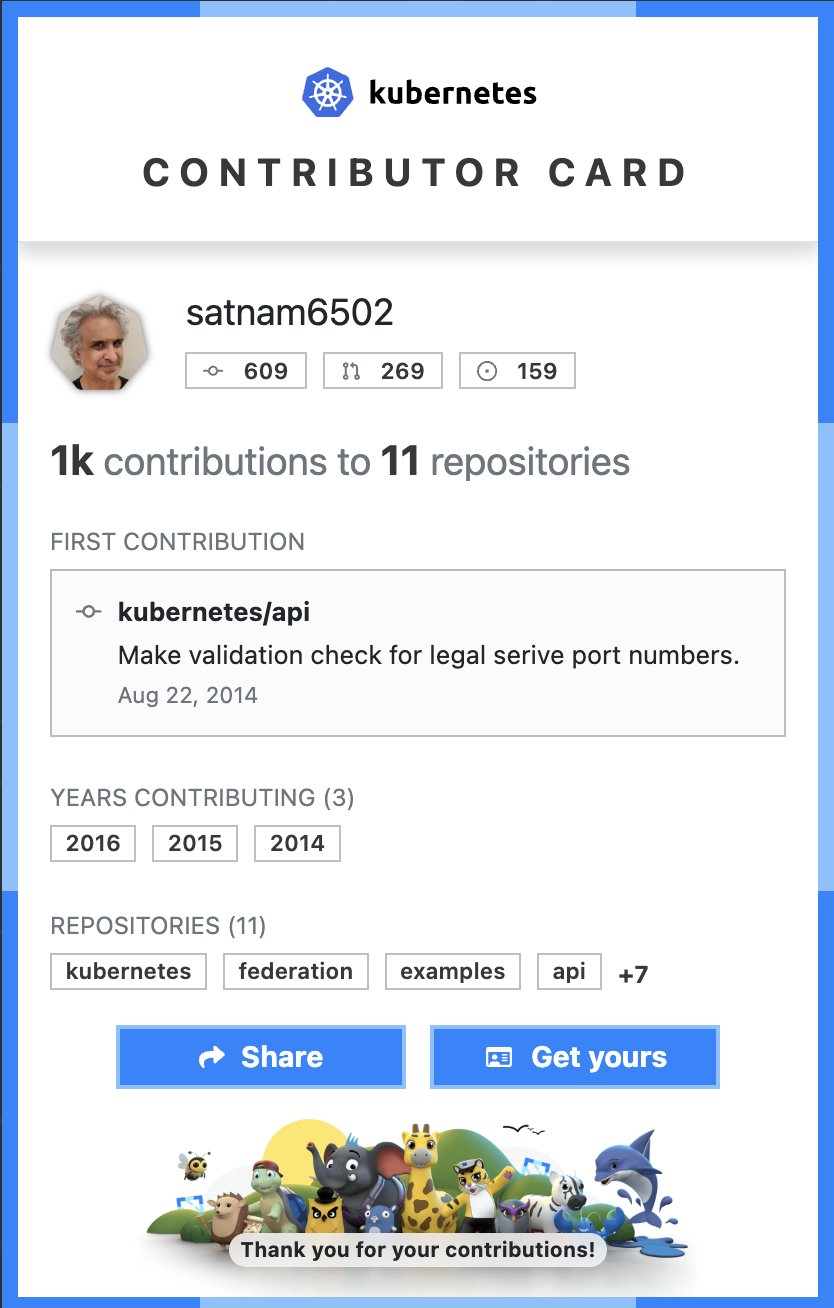

My research interests include functional programming in Haskell, high level techniques for hardware design (Lava, Bluespec, DSLs in Haskell, Esterel, Coq, Agda and C#), formal methods (SAT-solvers, model checkers, theorem provers), formally verified hardware/software co-design, FPGAs, and concurrent and parallel programming. I was an early member of the Kubernetes team at Google. I have served on the programme committees of several academic conferences including POPL, ICFP, CAV, FMCAD, DAC, FPGA, FCCM and EuroSys[https://www.eurosys.org].

I am a Senior Member of the ACM and IEEE and a Fellow of the IET. I am also an elected member of IFIP WG2.8 (functional programming) and IFIP WG2.11 (program generation). I previously served as an elected member of ACM SIGPLAN. I have held part-time or honorary positions at The University of Birmingham, Imperial College London, the University of Washington, and the University of Santa Cruz. I am currently a visiting academic at the Department of Computer Science and Technology at the University of Cambridge and the Department of Computing Science at the University of Glasgow.

I have professional software development experience in several programming languages including C++, C#, F#, Go, Java, Python, Ada, Pascal, Haskell, Bluespec, BASIC, Rocq (Coq), VHDL, SystemVerilog, Perl and PROLOG. I have also programmed in Miranda, Modula-2, Oberon, BCPL, C, Esterel, ML, LazyML, Occam, Agda, FORTH, FORTRAN, LISP and in serval assembly languages including 6502, 68000 and 32000.

Employment

| Employer | Role and Location |

|---|---|

| 2021 — 2025 | Fellow, Groq Mountain View, California |

| 2019 — 2021 | Software Engineer, Google Research (formerly Google AI) Mountain View, California, USA Also Lecturer at UC Santa Cruz, Jack Baskin School of Engineering |

| 2017 — 2019 | Software Engineer, Google X Mountain View, California, USA |

| 2015 — 2017 | Software Engineer, Facebook Menlo Park, California, USA |

| 2012 — 2015 | Software Engineer, Google Mountain View, California, USA |

| 2006 — 2011 | Researcher, Microsoft Research Cambridge, UK Also Professor of Reconfigurable Systems University of Birmingham Visiting Lecturer Imperial College, London |

| 2004 — 2006 | Principal Architect, Microsoft Redmond, Washington, USA Also Affiliate faculty at EE University of Washington (2005) |

| 1998 — 2004 | Principal Engineer, Xilinx San Jose, California, USA |

| 1991 - 1997 | Lecturer (Assistant Professor) Dept. Electrical Engineering Department, then Computing Science Department University of Glasgow, UK Also Consultant, Requirements Reuse British Telecom London and Ipswich, UK (1992 - 1993) Software Engineer (GUI development and Hardware Synthesis) Compass Design Automation / VLSI Technology Sophia Antipolis, France (1992) |

| 1987 - 1987 | Programmer (Unix, C) European Silicon Structures Bracknell, UK |

| 1986 - 1986 | Programmer (MS-DOS, Turbo Pascal) Glasgow Dental Hospital, Glasgow, UK |

Education

| When | What |

|---|---|

| 1983 — 1987 | BSc (Hons) Computing Science University of Glasgow, UK |

| 1987 — 1990 | PhD Computing Science University of Glasgow, UK |

Publications (81 in total)

Accelerator Compiler for the VENICE Vector Processor - Zhiduo Liu, Aaron Severance, Guy G.F. Lemieux, Satnam Singh. FPGA 2012, Monterey. ACM, 2012.

Resource-bounded multicore emulation using Beefarm - Oriol Arcas, Nehir Sonmez, Gokhan Sayilar, Satnam Singh, Osman S. Unsal, Adrian Cristal, Ibrahim Hur, Mateo Valero. Journal of Microprocessors and Microsystems, 2012.

From Plasma to BeeFarm: Design Issues and Experience of an FPGA-based Multicore Prototype - Oriol Arcas, Adrian Cristal, Ibrahim Hur, Satnam Singh, Nehir Somez. 7th International Symposium on Applied Reconfigurable Computing (ARC 2011). Springer Verlag, March 23, 2011.

The RLOC is Dead – Long Live the RLOC - Satnam Singh. ACM/SIGA International Symposium on Field Programmable Gate Arrays (FPGA). ACM, February 27, 2011.

TMbox: A Flexible and Reconfigurable 16-core Hybrid Transactional Memory System - Oriol Arcas, Adrian Cristal, Ibrahim Hur, Otto Pflücker, Satnam Singh, Nehir Somez, Osman Unsal. FPGAs for Custom Computing Machines 2011. IEEE Computer Society, May 1, 2011.

Reconfigurable Data Processing for Clouds - Anil Madhavapeddy, Satnam Singh. FPGAs for Custom Computing Machines 2011, May 2, 2011.

An Analysis of Programmer Productivity versus Performance for High Level Data Parallel Programming - Alexander Cole, Alistair McEwan, Satnam Singh. Communicating Processor Architectures. Elsevier, June 19, 2011.

Distributing C# Methods and Threads over Ethernet-connected FPGAs using Kiwi - David Greaves, Satnam Singh. Ninth ACM/IEEE International Conference on Formal Methods and Models for Codesign. IEEE, July 11, 2011.

Compiling Affine Recursion into Static Hardware - Dan Ghica, Alex Smith, Satnam Singh. The 16th ACM SIGPLAN International Conference on Functional Programming. ACM, September 19, 2011.

Computing Without Processors - Satnam Singh. Communications of the ACM, August 2011.

Designing Hardware with Dynamic Memory Abstraction - Jiří Šimša, Satnam Singh. ACM/SIGA International Symposium on Field Programmable Gate Arrays (FPGA). Association for Computing Machinery, Inc., February 22, 2010.

FPGA Circuit Synthesis of Accelerator Data-Parallel Programs - Barry Bond, Kerry Hammil, Lubomir Litchev, Satnam Singh. FPGAs for Custom Computing Machines. IEEE Computer Society, May 3, 2010.

Designing Application Specific Circuits with Concurrent C# Programs - David Greaves, Satnam Singh. Eighth ACM/IEEE Intl. Conference on Formal Methods and Models for Codesign. IEEE, July 26, 2010.

A Tutorial on Parallel and Concurrent Programming in Haskell - Simon Peyton Jones, Satnam Singh. Advanced Functional Programming Summer School 2008. LNCS, 2009.

A Bluespec Implementation of an FPGA-based Photoshop Plug-In - Satnam Singh. Hardware Design and Functional Languages 2009 (an ETPAS workshop), March 2009.

Synthesis of a Parallel Smith-Waterman Sequence Alignment Kernel into FPGA Hardware - Satnam Singh, David Greaves, Sutirtha Sanyal. Many-Core and Reconfigurable Supercomputing Conference 2009, Berlin, March 2009.

Exploiting System-Level Concurrency Abstractions for Hardware Descriptions - David J. Greaves, Satnam Singh. Microsoft Technical Report number MSR-TR-2009-48, April 22, 2009.

Design and Verification of Peripheral Control Circuits in Esterel - Satnam Singh. Journal of Concurrency and Computation: Practice and Experience, Wiley, 2009.

Parallel Performance Tuning for Haskell - Don Jones Jr., Simon Marlow, Satnam Singh. ACM SIGPLAN 2009 Haskell Symposium, Edinburgh. Association for Computing Machinery, Inc., September 3, 2009.

Runtime Support for Multicore Haskell - Simon Marlow, Simon Peyton Jones, Satnam Singh. International Conference on Functional Programming (ICFP) 2009. Association for Computing Machinery, Inc., September 5, 2009.

Finding heap-bounds for hardware synthesis - Byron Cook, Ashutosh Gupta, Stephen Magill, Andrey Rybalchenko, Jiří Šimša, Satnam Singh, Viktor Vafeiadis. Formal Methods in Computer Aided Design (FMCAD), Austin, November 15, 2009.

Kiwi: Synthesis of FPGA Circuits from Parallel Programs - David Greaves, Satnam Singh. IEEE Symposium on FPGAs for Custom Computing Machines (FCCM), Palo Alto, April 2008.

A Deterministic Multi-Way Rendezvous Library for Haskell - Stephen Edwards, Satnam Singh, Nalini Vasudevan. IEEE International Parallel and Distributed Processing Symposium (IPDPS), Miami, April 2008.

Describing Hardware with Parallel Programs - David Greaves, Satnam Singh. Designing Correct Circuits (DCC), Budapest, 2008.

Using C# Attributes to Describe Hardware Artefacts within Kiwi - David Greaves, Satnam Singh. Forum on Design Languages (FDL), 2008.

Declarative Programming Techniques for Many-Core Architectures - Satnam Singh. Hardware Design and Functional Languages, 2007.

Integrating FPGAs in High-Performance Computing: Programming Models for Parallel Systems – The Programmer’s Perspective - Satnam Singh. ACM/SIGA International Symposium on Field Programmable Gate Arrays (FPGA). Association for Computing Machinery, Inc., February 2007.

Hardware/Software Synthesis and Verification using Esterel - Satnam Singh. CPA 2007.

New Parallel Programming Techniques for Hardware Design - Satnam Singh. WG 10.5 International Conference on Very Large Scale Integration, Atlanta, GA. October 15-17, 2007.

Feedback Directed Implicit Parallelism - Tim Harris, Satnam Singh. International Conference on Functional Programming (ICFP) 2007, Freiburg, October 2007.

Lock Free Data Structures using STMs in Haskell - Anthony Discolo, Tim Harris, Simon Marlow, Simon Peyton Jones, Satnam Singh. Eighth International Symposium on Functional and Logic Programming, Fuji Susono, Japan, April 2006.

Higher Order Combinators for Join Patterns using STM - Satnam Singh. First ACM SIGPLAN Workshop on Languages, Compilers, and Hardware Support for Transactional Computing (TRANSCAT), June 2006.

Digital CAD Tools as Transactional Memory Workloads - Satnam Singh. Workshop on Transactional Memory Workloads, June 2006.

An Asynchronous Messaging Library for C# - Gerogio Chrysanthakopoulos, Satnam Singh. Synchronization and Coordination in Object Orientated Languages. An OOPSLA workshop, San Diego, October 2005.

A Demonstration of Co-Design and Co-Verification in a Synchronous Language - Satnam Singh. Design, Automation and Test in Europe (DATE), Paris, 2004.

Designing Reconfigurable Systems in Lava - Satnam Singh. Keynote speech at the reconfigurable systems track of VLSI Design 2004, Mumbai, 2004.

Functional Hardware Description in Lava - Koen Claessen, Mary Sheeran, Satnam Singh. Book chapter in The Fun of Programming. Palgrave, 2003.

System Level Specification in Lava - Satnam Singh. Design, Automation and Test in Europe (DATE), Munich, 2003.

An approach to compiling Cryptol to FPGAs - John Launchbury, Satnam Singh. 3rd Annual High Confidence Software and Systems Conference, Proceedings. Galois Connections and Xilinx, April 2003, pp. 137-146.

Design and Verification of CoreConnect IP using Esterel - Satnam Singh. The 12th Advanced Research Working Conference on Correct Hardware Design and Verification Methods (CHARME 2003), L’Aquila, Italy. Springer-Verlag, 2003.

System Level Design and Verification Using a Synchronous Language - Gérard Berry, Michael Kishinevsky, Satnam Singh. The International Conference on Computer Aided Design, 2003.

Lava: An Embedded Language for Structural Hardware Design - Koen Claessen, Mary Sheeran, Satnam Singh. Designing Correct Circuits, Grenoble, France, April 2002.

Using Lava to Design and Verify Recursive and Periodic Sorters - Koen Claessen, Mary Sheeran, Satnam Singh. International Journal on Software Tools for Technology Transfer, 2002.

Types for Describing Dynamic Reconfiguration - Satnam Singh. The International Conference on Computer Aided Design, 2002.

Lava and JBits: From HDL to Bitstream in Seconds - Satnam Singh, Phil James-Roxby. IEEE Symposium on FPGAs for Custom Computing Machines 2001. Eds. K.L. Pocek and J.M. Arnold, IEEE Computer Society Press, 2001.

Rapid Construction of Partial Configuration Datastreams from High Level Constructs using JBits - Satnam Singh, Phil James-Roxby. Field-Programmable Logic and Applications. Springer-Verlag LNCS, August 2001.

The Design and Verification of a Sorter Core - Koen Claessen, Mary Sheeran, Satnam Singh. CHARME’2001, Livingston, Scotland. Springer-Verlag LNCS, September 2001.

The Lava HDL for FPGA Design - Satnam Singh, Mary Sheeran. HDLCON’2000, San Jose, 2000.

Death of the RLOC? - Satnam Singh. FCCM’2000, Napa, California. IEEE Computer Society Press, 2000.

Formal Verification of FPGA Cores - Carl Johan Lillieroth, Satnam Singh. Nordic Journal of Computing, April 2000.

Checking safety properties using induction and a SAT-solver - Mary Sheeran, Satnam Singh, Gunnar Stalmarck. Formal Methods in Computer Aided Design (FMCAD), Austin, November 2000.

Dynamic Specialisation of XC6200 FPGAs by Partial Evaluation - Nicholas McKay, Satnam Singh. FPL’98, Talin, Estonia. Springer-Verlag LNCS 1706, 1999.

Formal Verification of FPGA Cores - Carl Johan Lillieroth, Satnam Singh. Nordic Journal of Computing, 6:299-310, 1999.

Bezier Curve Rendering on Virtex™ - Donald MacVicar, Satnam Singh, Robert Slous. FCCM’99, Napa, California. IEEE Computer Society Press, 1999.

Rendering PostScript™ Fonts on FPGAs - Donald MacVicar, Satnam Singh. FPL’99, Glasgow, UK. Springer-Verlag LNCS, 1999.

Debugging Techniques for Dynamically Reconfigurable Hardware - Nicholas McKay, Satnam Singh. FCCM’99, Napa, California. IEEE Computer Society Press, 1999.

Photoshop Acceleration using Virtex - Satnam Singh, Stefan Ludwig. FPL’99, Glasgow, UK. Springer-Verlag LNCS, 1999.

Formal Verification of Reconfigurable Cores - Satnam Singh, Carl Johan Lillieroth. FCCM’99, Napa, California. IEEE Computer Society Press, 1999.

Accelerating Adobe Photoshop with Reconfigurable Logic - Satnam Singh, Robert Slous. FCCM’98, Napa, California. IEEE Computer Society Press, 1998.

Applications of Run-Time Specialisation for FPGAs - Nicholas McKay, Satnam Singh. FCCM’98, Napa, California. IEEE Computer Society Press, 1998.

Accelerating DTP with Reconfigurable Computing Engines - Donald MacVicar, Satnam Singh. FPL’98, Talin, Estonia. Springer-Verlag, 1998.

Lava: Hardware Design in Haskell - Per Bjesse, Koen Claessen, Mary Sheeran, Satnam Singh. ICFP’98. Springer-Verlag LNCS, 1998.

Partial Evaluation of Hardware - Satnam Singh, Nicholas McKay. Partial Evaluation Summer School 98, Copenhagen, Denmark. Springer-Verlag LNCS, 1998.

Dynamic Specialisation of XC6200 FPGAs by Partial Evaluation - Nicholas McKay, T. F. Melham, K.W. Susanto, Satnam Singh. Proceedings of the IEEE Symposium on FPGAs for Custom Computing Machines, 1998.

Formal Methods for Intellectual Property - Carl Johan Block, Satnam Singh. Nordic Formal Methods Workshop 98, Turku, Finland, 1998.

A Dynamic Reconfiguration Run-Time System - Jim Burns, Adam Donlin, Jonathan Hogg, Satnam Singh, Mark de Wit. FCCM’97, Napa, California. IEEE Computer Society Press, 1997.

New HDL Research Challenges posed by Dynamically Reprogrammable Hardware - Jonathan Hogg, Satnam Singh, Mary Sheeran. APCHDL’96, Bangalore, January 1996.

Expressing Dynamic Reconfiguration by Partial Evaluation - Satnam Singh, Jonathan Hogg, Derek McAuley. FCCM’96, Napa, California. IEEE Computer Society Press, 1996.

Architectural Descriptions for FPGAs - Satnam Singh. FCCM’95, Napa, California. IEEE Computer Society Press, 1995.

Ruby as a basis for Hardware/Software Co-Design - Mary Sheeran, Satnam Singh. IEE Symposium on Hardware/Software Co-Design. IEE, London, October 1995.

Virtual Hardware for Graphics Applications using FPGAs - Satnam Singh, Pierre Bellec. FCCM’94, Napa, California. IEEE Computer Society Press, 1994.

Accelerating Graphics using FPGAs - Satnam Singh, Pierre Bellec. Canadian Workshop on Field-Programmable Devices, Kingston. June 13-16, 1994.

Designing Graphical User Interfaces for Haskell - Satnam Singh, Alastair Reid. Glasgow Functional Programming Workshop, Ayr. Springer-Verlag, 1993.

Hardware Synthesis Techniques for Algebraic HDLs - Satnam Singh. SASIMI’93, Nara, Japan, 1993.

Circuit Analysis by Non-Standard Interpretation - Satnam Singh. Second IFIP WG10.2/WG10.5 Workshop on Designing Correct Circuits, Lyngby, Denmark. North-Holland, 1992.

Circuit Layout using NSI - Satnam Singh. Advanced Research Workshop on Correct Hardware Design Methodologies, Turin. North-Holland, 1991.

An X11/XView Interpreter for Miranda - Satnam Singh. Glasgow Functional Programming Workshop, Portree. Springer-Verlag, 1991.

Analysis of Hardware Descriptions - Satnam Singh. PhD Thesis, University of Glasgow, 1991.

Differentiating Strictness - Satnam Singh. Glasgow Functional Programming Workshop, Ullapool. Springer-Verlag, 1990.

Implementation of a Non-Standard Interpretation System - Satnam Singh. Glasgow Functional Programming Workshop, Fraserburgh. Springer-Verlag, 1989.

Application of Non-Standard Interpretation: Testability - Satnam Singh. Design of Correct VLSI Circuits. Proc. IFIP-IMEC Workshop, Belgium. North Holland, 1989.

Posts

Formally Verifying Hardware with Aristotle, Harmonic's AI Theorem Prover (talk at Imperial College London)

My SIGPLAN Current Continuation YouTube Interview. 29 May 2025

My Haskell Interlude Podcast Interview. 26 August 2024

My Type Theory for All Podcast Interview. 15 August 2024

Accelerating Large Language Models with Groq's LPU Machine Learing Chips. 26 July 2024

Obiturary for Ross Anderson. 6 April 2024

Silver Oak: Building A High Assurance Silicon Root of Trust. 13 March 2024

Abuse and Bullying: An Ad Hoc Personal Survival Guide. 15 January 2023

Advice for Whiteboard Coding Interviews. 3 October 2021.

Cluster Level Logging with Kubernetes. 11 June 2015

Cluster Management with Kubernetes. 5 June 2015

Logging Kubernetes Pods using Fluentd and Elasticsearch. 18 November 2014

Creating a Windows DLL from a Haskell Program and calling it from C++. 19 April 2011

Compiling C# Programs to FPGA Circuits: An Ethernet Packet Processing Example. 15 February 2011

Using the Virtex-6 Embedded Tri-Mode Ethernet MAC Wrapper v1.4 with the ML605 Board. 11 February 2011

Reconfigurable Data Processing for Clouds. 18 January 2011

F# Black-Scholes running on GPUs and SSE3 Multicore Processors using Accelerator. 14 October 2010

Kiwi Synthesis of C# and F# Combinational Circuit Models into FPGA Circuits. 28 April 2010

A C# implementation of a convolver using Accelerator for GPGPU and multicore targets using LINQ operators. 11 January 2010

An F# Functional Geometry Description of Escher's Fish. 5 January 2010

GPGPU and x64 Multicore Programming with Accelerator from F#. 15 December 2009

Postcard From The Valley. 21 February 1998.